GL852G is Genesys Logic’s premium 4-port Hub solution which fully complies with Universal Serial Bus Specification Revision 2.0. GL852G implements multiple TT* (Note1) architecture that provide dedicated TT* to each downstream (DS) ports, which guarantee Full-Speed(FS) data passing bandwidth when multiple FS device perform heavy loading operations. The controller inherits Genesys Logic’s cutting edge technology on cost and power efficient serial interface design. GL852G has proven compatibility, lower power consumption figure and better cost structure above all USB2.0 hub solutions worldwide.

GL852G implements multiple hub configuration features onto internal mask ROM, which traditionally requires one external EEPROM. The microprocessor detects general purpose I/O (GPIO) status during the initial stage to configure hub settings such as (1) number of DSport, (2) declare of compound device (3) gang/individual mode selection…etc. External EEPROM can be removed if no vendor specified PID/VID or product string is required for the application.

GL852G supports four package types, summarized as below table. LQFP48 package provides full hub features such as (1) two-color (green/amber) status LEDs for each DS ports, (2) Individual/Gang mode power management scheme that indicates DS port over-current events. (3) Number of DS ports setting configured by GPIO setting (4) non-removable declaration configured by GPIO setting (5) Support both 93C46 and 24C02 EEPROM (6) power switch polarity selections…etc. QFN28 package support only partial hub features but provide smaller footprint (5x5mm) that targets space limited PCB layout environments such as embedded system or UMPC/MID applications.

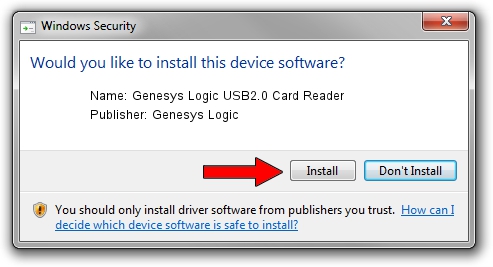

Download any of the past six PureConnect releases and patches. Utilities and Downloads This is a public page within the resource center that lists the PureConnect utilities and provides links to the secure files. Intel Android device USB driver 1.10.0 on 32-bit and 64-bit PCs. This download is licensed as freeware for the Windows (32-bit and 64-bit) operating system on a laptop or desktop PC from drivers without restrictions. Intel Android device USB driver 1.10.0 is available to all software users as a free download for Windows.

| Package type | # of DS ports | Port # config. | Non-removable Declaration | Power mgmt. | LED support | EEPROM |

|---|---|---|---|---|---|---|

| 48LQFP | 4 | GPIO | EEPROM/GPIO | Individual/Gang | Green/Amber | 93C46/ 24C02 |

| 28QFN | 4 | EEPROM | EEPROM | Individual/Gang | N/A | 24C02 |

*Note: TT (transaction translator) is the main traffic control engine in an USB 2.0 hub to handle the

unbalanced traffic speed between the upstream port and the downstream ports.

● Compliant to USB specification Revision 2.0

− 4 downstream ports

− Upstream port supports both high-speed (HS) and full-speed (FS) traffic

− Downstream ports support HS, FS, and low-speed (LS) traffic

− 1 control pipe (endpoint 0, 64-byte data payload) and 1 interrupt pipe (endpoint 1, 1-byte data payload)

− Backward compatible to USB specification Revision 1.1

●On-chip 8-bit micro-processor

− RISC-like architecture

− USB optimized instruction set

− Dual cycle instruction execution

− Performance: 6 MIPS @ 12MHz

− With 64-byte RAM and 2K internal ROM

− Support customized PID, VID by reading external EEPROM

− Support downstream port configuration by reading external EEPROM

●Multiple Transaction translator (MTT)

− MTT provides respective TT control logics for each downstream port.

●Each downstream port supports two-color status indicator, with automatic and manual modes compliant to USB specification Revision 2.0

●Built-in upstream port 1.5K0001 pull-up and downstream port 15K pull-down resistors

●Support both individual and gang modes of power management and over-current detection for downstream ports

●Conform to bus power requirements of USB 2.0 specification

●Automatic switching between self-powered and bus-powered modes

●Integrate USB 2.0 transceiver

●Embedded PLL support external 12 MHz crystal / Oscillator clock input

●Optional 27/48 MHz Oscillator clock input (Not available on QFN 28 package)

●Support compound-device (non-removable in downstream ports) by I/O pin configuration (Not available on QFN 28 package)

●Number of Downstream port can be configured by GPIO without external EEPROM (Not available on QFN 28 package)

●Operate on 3.3 Volts (Built-in 3.3V to 1.8V regulator)

●Improve output drivers with slew-rate control for EMI reduction

●Internal power-fail detection for ESD recovery

●Available package type: 48-pin LQFP and 28-pin QFN

●Applications:

− Stand-alone USB hub / USB Docking

− UMPC/MID, motherboard on-board applications

− Consumer electronics built-in hub application

− Monitor built-in hub

− Embedded systems

− Compound device to support USB HUB function such as keyboard hub applications

Download Genesys Software

Genesys GL3523 is a 4-port, low-power, and configurable hub controller. It is compliant with the USB 3.1 specification. GL3523 integrates Genesys Logic self-developed USB 3.1 Gen 1 Super Speed transmitter/receiver physical layer (PHY) and USB 2.0 High-Speed PHY. It supports Super Speed, Hi-Speed, and Full-Speed USB connections and is fully backward compatible to all USB 2.0 and USB 1.1 hosts. GL3523 also implements multiple TT architecture providing dedicated TT to each downstream (DS) port, which guarantees Full-Speed(FS) data passing bandwidth when multiple FS devices perform heavy loading operations. Furthermore, GL3523 has built-in 5V to 3.3V and 5V to 1.2V regulators, which saves customers’ BOM cost, and eases for PCB design.

GL3523 features the native fast-charging and complies with USB-IF battery charging specification rev1.2, it could fast-charge Apple, Samsung Galaxy devices, and any device complaint with BC1.2/1.1. It also allows portable devices to draw up to 1.5A from GL3523 charging downstream ports (CDP) or dedicated charging port (DCP). It can enable systems to fast charge handheld devices even during “Sleep” and “Power-off” modes.

Download Genesys Input Devices Driver

- Compliant with USB 3.1 Gen 1 Specification

- Upstream port supports SuperSpeed (SS), HighSpeed (HS) and FullSpeed (FS) traffic

- Downstream ports support SS, HS, FS, and LowSpeed (LS) traffic

- 1 control pipe and 1 interrupt pipe

- Backward compatible to USB specification Revision 2.0/1.1

- Native USB Type-C support in GL3523-S series

- Compliant with USB Type-C Cable and Connection Specification Revision 1.0

- Featuring USB Type-C functions

- Detecting flip-able/reversible plugging

- Discovering/configuring VBUS

- Supporting USB Type-C Current modes , including USB Default, 1.5A@5V, 3A@5V

- Configuring/Supporting VCONN Power and having VCONN over-current protection

- Featuring fast-charging on all downstream ports and upstream port

- Compliant with USB Battery Charging Revision v1.2, supporting CDP, DCP, and ACA-Dock

- Downstream ports can be turned from a Standard Downstream Port (SDP) into Charging Downstream Port (CDP) or Dedicated Charging Port (DCP)

- Downstream devices can be charged while upstream VBUS is not present, which can be applied on wall charger applications

- Upstream port is capable of charging and data communicating simultaneously for portable devices supporting ACA-Dock or proprietary charging protocols

- Supporting Apple 1A/2.1A/2.4A and Samsung Galaxy devices fast-charging

- On-chip 8-bit micro-processor

- RISC-like architecture

- USB optimized instruction set

- 1 cycle instruction execution (maximum)

- Performance: 12 MIPS @ 12.5MHz (maximum)

- With 256-byte RAM, 20K-byte internal ROM, and 24K-byte SRAM

- Multiple Transaction Translator (TT) architecture

- Providing dedicated TT control logics for each downstream port

- Superior performance when multiple FS devices operate concurrently

- Integrated USB transceiver

- Improving output drivers with slew-rate control for EMI reduction

- Internal power-fail detection for ESD recovery

- Advanced power management and low power consumption

- Supporting USB 3.1 U0/U1/U2/U3 power management states

- Supporting USB Link Power Management (LPM) L0/L1/L2

- Supporting individual/gang mode over-current detection for all downstream ports

- Supporting both low/high-enabled power switches

- Patented Smart Power Management

- Configurable settings by firmware in SPI flash

- Configurable charging port

- Configurable 4/3/2 downstream ports, downstream port can be disabled/enabled by each specific port for USB3.1/USB2.0

- Configurable Upstream and Downstream Ports in GL3523-S

- Supporting multiple upstream ports in GL3253-S OV3S1 and OV5S1 packages

- Supporting full in-system programming firmware upgrade by SPI-flash and configuration by EEPROM

- Supporting compound-device (non-removable setting on downstream ports)

- Supporting customization VID/PID

- Flexible design

- Supporting Poly-fuse/Power-switch

- Automatic switching between self-powered and bus-powered modes

- Supporting electrical tuning for each specific port

- Supporting programmable breathing LED

- Supporting register setting by firmware

- Supporting vendor command and SMBUS

- Allow downstream ports to connect up to 8 devices, 4 x USB3.1 non-removable devices with 4 x USB2.0 non-removable devices or exposed ports

- Low BOM cost

- Single external 25 MHz crystal / Oscillator clock input

- Built-in upstream port 1.5KΩ pull-up and downstream port 15KΩ pull-down resistors

- Built-in 5 to 3.3V and 5 to 1.2V regulator

- Different package types available for various applications

- Applications

- Standalone USB hub/Docking station

- Tablet/Ultrabook/NB

- Motherboard

- Monitor built-in hub, GPIOs can be programmed as I2C interface to easily update scalar firmware through USB interface

- TV built-in hub

- Compound device, such as hub-reader application

- USB wall charger

- Other consumer electronics

- Customized applications

- Dynamically disable/enable ports

- GPIO signaling of ambient light sensor or rotation/position sensor